# Intel<sup>®</sup> X557-AT/AT2/AT4 10 GbE PHY Datasheet

### **Networking Division (ND)**

### Features:

- 10GBASE-T Performance Ability to support worst case channels while reducing power and latency when channel characteristics permit:

- 100 m on augmented CAT 6 (CAT 6A and CAT 7)

- 55 m on CAT 6 and best-effort using CAT 5e

- Built-in thermal management capabilities Enables deployment in thermally constrained environments

- On-die thermal sensor with alarm and warning thresholds

- **Note:** Details describing built-in thermal management capabilities will be made available in a future datasheet release.

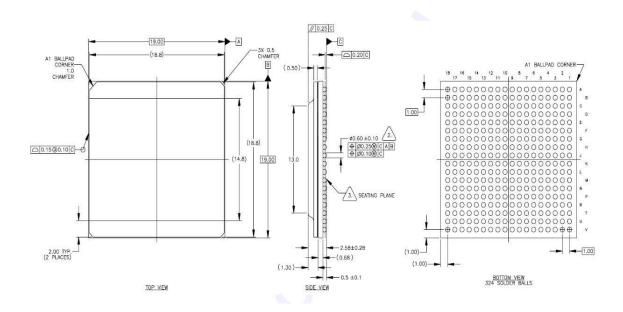

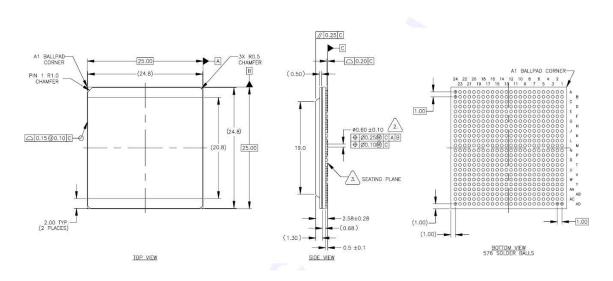

- 19 x 19 mm (single/dual port) or 25 x 25 mm (quad port) flip-chip BGA or package Low cost, flexible heat-sinking, and compatible with volume PCB manufacturing:

- 1 mm ball pitch

- Low thermal resistance  $(\theta_{ic})$

- IEEE

802.3an-2008 compliant auto-negotiation Interoperability with existing Ethernet infrastructure

- External SPI Flash interface

- High-Performance full KR (with auto-negotiation) / XFI / SGMII I/F with AC-JTAG- Ensures troublefree operation over a range of interconnect scenarios

- Loopback Capability Enables extensive system test and debug with remote loopback control

- Supports numerous loopbacks with pass-through capability

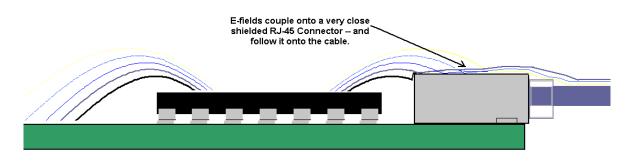

- Integrated MDI Filter and Advanced RFI Cancellation Patented RFI technology provided improved performance in the presence of RF interference

- Eliminates external filter components

Order Number: 334279-002 Revision 2.2 June 2017

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.

The products and services described may contain defects or errors which may cause deviations from published specifications. Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting www.intel.com/design/literature.htm.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

\* Other names and brands may be claimed as the property of others.

© 2017 Intel Corporation.

### **Revision History**

| Revision | Date       | Comments                                                                                                                          |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 2.2      | June 2017  | Update Bill Of Material (BOM) - added new Flash components.                                                                       |

| 2.1      | April 2016 | <ul><li>Corrected minor pin table information.</li><li>Updated power and peak current information.</li><li>Updated BOM.</li></ul> |

| 2.0      | April 2015 | First release (Intel Public).                                                                                                     |

NOTE: This page intentionally left blank.

# 1.0 Overview

### 1.1 Introduction

The Intel® X557-AT/AT2/AT4 10 GbE PHY (X557) is a single (AT), dual (AT2), quad (AT4) port, 28 nm CMOS 10GBASE-T / 1000BASE-T / 100BASE-TX triple-speed PHY that is designed to be a low-power solution for all Network Interface Cards (NICs), switch, and LAN on Motherboard (LOM) applications that require 10GBASE-T capability.

This section is intended to provide an overview of the X557 and its operating modes.

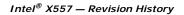

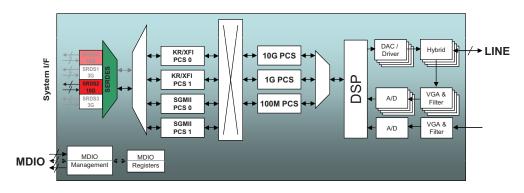

A block diagram of the X557 is shown in Figure 1-1. Each port uses a common analog front-end for all three modes of operation as well as a common system interface (configurable as dual KR/XFI in 10 GbE,1000BASE-X for GbE and dual SGMII in 1 GbE / 100 Mb/s). In the 10 GbE mode transmit direction, data from the system interface is equalized and received. This data is then mapped into a virtual internal SGMII interface where blocks of two SGMII frames (32 bits of data + 4 bits of control) are encoded into a single 65-byte block, using the 64-byte/65-byte encoding scheme specified in Clause 55. In 10 GbE mode, 50 of these65-byte blocks are aggregated together, along with a prepended auxiliary bit, and an appended CRC-8to form the 3259-bit 10GBASE-T transmission frame payload. This payload is encoded using a combination of LDPC encoding and coset partitioning, with the LDPC encoding adding an additional 325systematic check bits to produce a 3584-bit 10GBASE-T transmission frame. The coset partitioning effectively divides the frame up into 512 7-bit symbols, where the upper 3 bits are uncoded and describe the coset, while the lower 4 bits are coded and identify an element within the coset. These 8cosets are then mapped onto a 128-DSQ constellation (a 16 x 16 checkerboard pattern) that is physically encoded as two back-to-back PAM-16 symbols. These symbols are then THP precoded, filtered, and sent out over the four twisted pairs in the cable.

#### Figure 1-1 Intel® X557 10 GbE PHY Block Diagram

In the receive direction in 10 GbE mode, PAM-16 coded symbols enter the X557 from the line interface and pass through the hybrid, which provides transmit / receive isolation. These symbols are then filtered and amplified prior to being sampled by four high-speed, high-precision A/D converters. The outputs of these A/D converters are then passed through an extensive set of adaptive equalizers that provide both cross-talk and echo cancellation. After timing is recovered, the data from the four channels is aligned and merged together to form the original, but noisy transmission frames. In 10 GbE mode, the data is decoded using an LDPC decoder. However, in 10 GbE mode the data is further sliced using knowledge of the coset partitioning and 128-DSQ mapping to produce the original 10GBASE-T transmission frame payload. The CRC-8 over this payload is then checked to ensure integrity of the uncoded bits. Finally, in all schemes, the auxiliary bit is stripped, the 65-byte blocks remapped into XGMII blocks, and the received Ethernet data transmitted out the MAC interface.

When operating in 1 GbE or 100 Mb/s modes, receive data from the analog front-end is routed to either the 1 GbE or 100 Mb/s PCS where timing is recovered and equalization performed. In 1 GbE mode, Viterbi decoding is also done. From here, the data passes across a virtual GMII interface to the system interface which is SGMII mode on logical Lane 0. In the transmit direction, 1 GbE or 100 Mb/s data is received on the SGMII interface, passed through the 1 GbE or 100 Mb/s PCS and then transmitted by the common analog front-end.

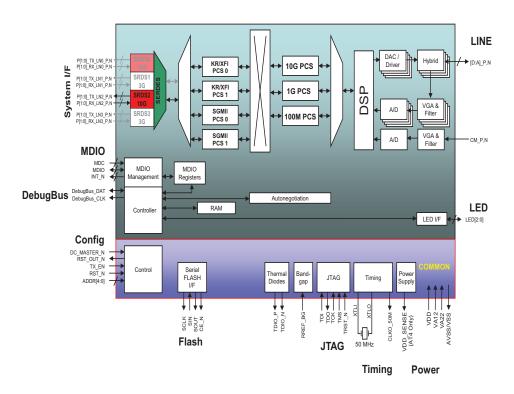

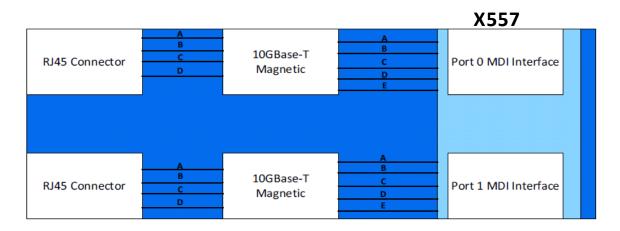

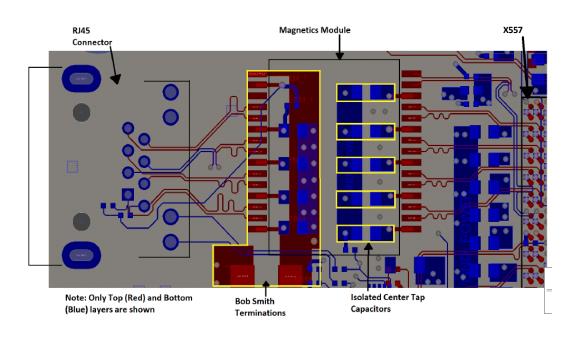

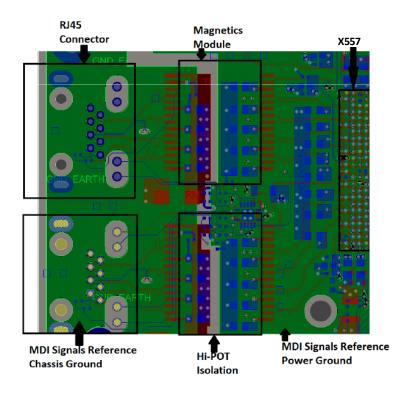

Figure 1-2 shows a typical system-level block diagram of a 10GBASE-T channel with an optional dualmedia interface built using the X557. On the line side of the X557, a robust interface providing good common-mode rejection and electrical protection against cable discharge is implemented. On the MAC side, the X557 provides a robust SerDes interface with configurable pre-emphasis and receive equalization. For test coverage, this interface also incorporates AC JTAG.

#### Figure 1-2 X557 10 GbE PHY Block Interconnect

On-chip, the X557 contains a 32-bit micro-controller that manages the state machines and operation of the various elements within the chip. Consequently, there is a great deal of flexibility afforded to the end user because of the presence of this micro-controller, and as such the X557 offers a high degree of control and flexibility. The image for the micro-controller is stored in an optional external SPI Flash. This interface also provides the user the capability of directly programming the Flash during manufacturing.

In addition to the Ethernet interfaces, the X557 provides three 20 mA LED outputs per port that are configurable via software to respond to a variety of conditions such as link activity and connection status. Clocking for the X557 is provided from a 50 MHz differential clock.

Power for the X557 is provided from three supply voltages, with configurable I/O voltage levels. In order to assist the system designer in deploying the X557, a reference design (part numbers, schematics, and layout) is provided that is optimized for performance, efficiency and cost.

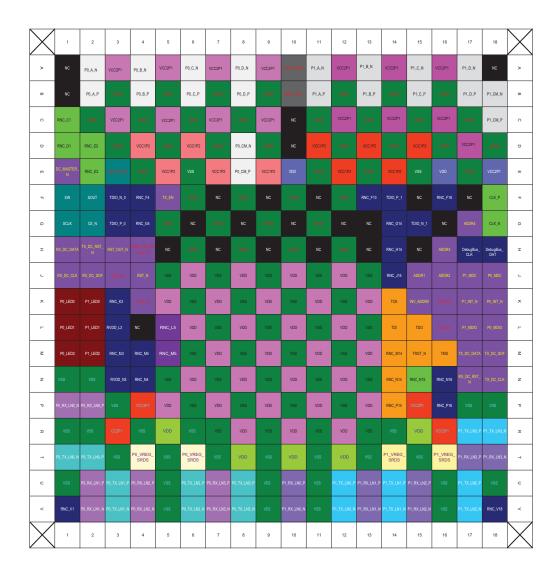

# 1.2 Mechanical

The X557 is packaged in a 19 mm x 19 mm flip-chip, 324-pin BGA (single and dual port) or a 25 mm x 25 mm flip-chip 576 pin BGA (quad port) along with a thermal heat spreader. Consequently, the  $\theta_{jc}$  is a low 0.42 °C/W. Meanwhile, the die is rated to operate up to 105 °C junction temperature, so engineering an appropriate thermal solution for the target system is a straight-forward task.

### 1.2.1 Power Supplies

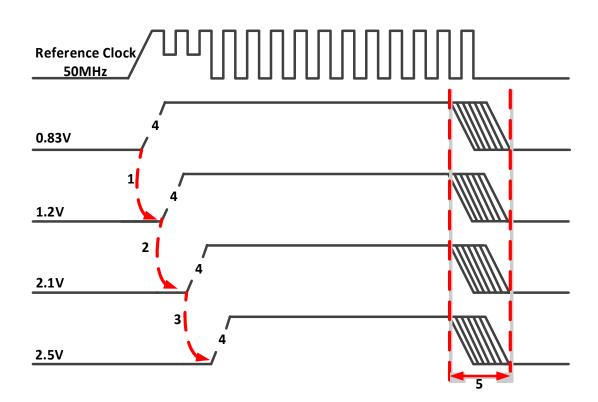

The X557 uses these power supplies: a 0.83V digital supply (VDD), 1.2V and 2.1V analog supplies (VA12 and VA21, respectively) and 2.5V digital I/O. From an operating perspective, no power supply sequencing is required, but it is recommended that all supplies come up following the directions provided in section within 20 ms from the first rail rising to the last rail reaching its 70% voltage level.

For I/O, the X557 offers a separate VDD\_IO supply, which sets the logic thresholds for the I/O at 70% / 30% of its voltage. In addition to the VDD\_IO supply voltage of 2.5V, a separate control pin (MDIO\_1P2\_SELECT\_N when pulled low) enables pins MDC, MDIO, TX\_EN (single/dual port only) and RST\_N to operate at 1.2V logic levels, regardless of the voltage on VDD\_IO.

AVSS, VSS, and VSS\_SRDS must be tied to the same ground plane.

### 1.2.2 Clocks

The X557-AT uses a 50 MHz differential clock to synthesize all required clocks.

Note: Either a 50 MHZ crystal or a 50 MHz oscillator can be implemented with the X557-AT (single port) device (crystal mode or oscillator mode, XTAL\_SELECT\_N = 0b or XTAL\_SELECT\_N = 1b). However, a 50 MHZ oscillator must be implemented for use with the X557-AT2 (dual port) and X557-AT4 (quad port) devices (LVDS oscillator mode).

### 1.2.3 Flash

The X557 is capable of operating with a 512 KB (4 Mb) or larger SPI serial Flash.

For Flash I/O, the X557 offers a separate VDD\_FLASH supply that is used to run the Flash interface. VDD\_FLASH requires 2.5V.

### 1.2.4 Power-on Default Values

The X557 has a fixed set of hardware default values that exist in the chip for all configurable registers. However, the firmware is capable of storing in its boot image any change to these defaults for up to 48 PHYs within a single image, effectively enabling the user to configure the chip to come out of reset in the desired operating state. This can be done by altering the boot image. Contact your Intel representative for more details about updating boot images.

### 1.2.5 SerDes Configuration

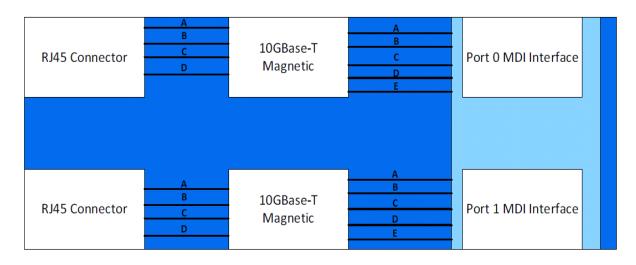

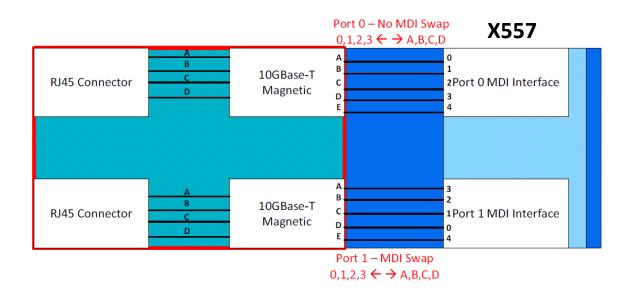

The X557 is capable of routing any logical SerDes lane to any physical SerDes lane as well as performing polarity inversions. On the line side, in addition to supporting MDI / MDI-X and automatic polarity correction, the X557 supports lane swapping of the A, B, C, and D pairs to enable easy board routing with different magnetics pinouts.

### 1.3 SerDes

The X557 is designed to be used in conjunction with a triple-speed MAC chip:

- KR/XFI for 10 GbE

- 1000BASE-X for 1 GbE (SerDes logical lane 0)

- SGMII for 100 Mb/s (SerDes logical lane 0)

- **Note:** The X557-AT2 10 GbE PHY internally has four SerDes per PHY, but only physical lane 2 is connected. Consequently, the register map contains information for lanes 0, 1 and 3, but these cannot be used in the X557-AT2. The X557 is capable of being configured so that the MAC interface can start in one of the following modes:

- 1. Start with the 10 GbE interface on KR/XFI.

- 2. Start with the 1000BASE-X interface on (SGMII without auto-negotiation).

- 3. Start with extended SGMII auto-negotiation enabled.

- 4. Start with all interfaces off.

Once a connection to a link partner has been established, the interface switches to the correct MAC interface speed.

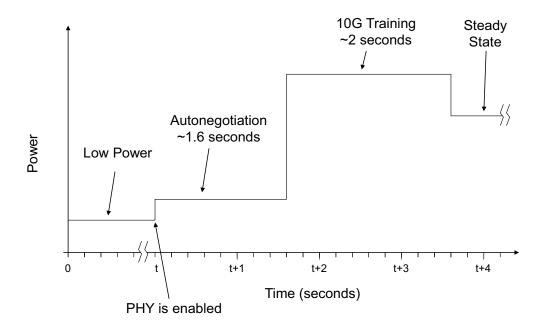

### 1.4 Power On

The X557 is designed to perform the following operations at boot:

- 1. Power-up calibration of the internal VCOs and variable power supplies (if variable supply operation is enabled).

- Provision stored default values. X557 is capable of storing in its firmware image a list of registers whose default values should be overwritten with a user-specified value on power up. Contact your Intel representative for more details about enabling the PHY to be personalized for certain modes of operation.

- 3. Calibration of the analog front-end.

- 4. Auto-negotiation.

- 5. Perform training (as required).

- 6. Verify error-free operation.

7. Enter steady state.

# 1.5 Cable Diagnostics

The X557 implements a powerful cable diagnostic algorithm to accurately measure all of the TDR and TDT (cross-channel impulse responses) sequences within the group of four channels. The algorithm used transmits a pseudo-noise sequence with an amplitude of less than 300 mV for a brief period of time, and from this converges the 10GBASE-T equalizers on all of the other channels. From the results of this measurement, the length of each pair, the top impairment along the pair, and the impedance of the cable are flagged. These measurements are reported to an accuracy to  $\pm 1$ m using a cable propagation characteristics of 4.83 ns/m and are presented in the global MMD register map.

# 1.6 Debug Tools

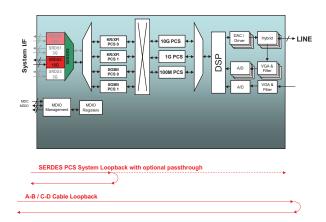

The X557 supports a full suite of network and system loopbacks at all 10 Gb/s rates. As well the X557 supports a network loopback with pass through and destructive merge, which means that the looped-back traffic is also passed through to the SerDes interface, as well looped back. In the transmit direction, any traffic on the SerDes interface is destructively merged with the loopback traffic. For example, the SerDes traffic takes priority over the looped-back traffic). This enables diagnosis of remote equipment while maintaining a remote session connection during a loopback test. Loopback is shown in Figure 1-3.

#### Figure 1-3 X557 Loopback

In addition to the loopbacks, the X557 supports CRC-32 packet checking on both the receive and transmit traffic at all rates, and maintains one second interval packet counters for both bad and good packets.

Finally, the X557 is able to generate all of the IEEE test mode patterns, as well as CRPAT generation and checking in both line and system directions.

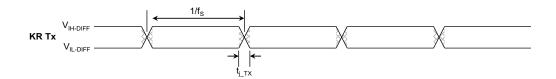

On the KR interface, the X557 supports  $x^9$ ,  $x^{31}$ , square wave, and pseudo-noise generation and checking, as well as CRPAT generation and checking.

# **1.7 Energy Efficient Ethernet (EEE)**

The X557 provides support for EEE on 10GBASE-T and 1000BASE-T interfaces. It is also capable of running in both normal operating mode, where the system controls entering and exiting from the EEE state and autonomous operation on the line where the PHY controls entering and exiting EEE operation via a provisioned no-traffic timer. If no traffic is seen within a certain period of time, the PHY goes to sleep on the line if connected at either 10 GbE or 1 GbE rates. This mode of operation requires the MACs to be in operation because rate pacing during startup is done via pause frames.

Intel<sup>®</sup> X557—Overview

NOTE: This page intentionally left blank.

# 2.0 Hardware Interfaces (X557-AT and X557-AT2)

Note: Any signal name that ends with an asterisk (\*) or pin name that ends with \_N are active low.

### 2.1 Management Interface

The management interface on the X557 is a two wire interface with a unidirectional MDC clock and a bidirectional MDIO data. The MDIO interface on the X557 is a robust implementation of this standard. It is designed to operate up to 18 MHz<sup>1</sup> and is capable of withstanding voltages up to double the operating voltage (the theoretical worst-case maximum reflection on an unterminated bus). It uses a Schmitt-trigger in conjunction with a de-bounce state machine to de-bounce the signals, and is capable of hot-insertion. The MDIO data line is capable of pulling low a 280  $\Omega$  load tied to 1.2V, and can be configured to support either open-drain, or push-pull operation in the Global General Provisioning 2: Address 1E.C441 register. Push-pull is the default operating mode.

In order to provide flexibility to the implementation, the X557 uses a programmable I/O voltage. The logic thresholds for the I/O are set at 70% and 30% for  $V_{IH}/V_{OH}$  and  $V_{IL}/V_{OL}$ , respectively for any VDD\_IO greater than 1.8V. For 1.2V MDIO operation (affects TX\_EN, MDC, MDIO, RST\_N) a separate signal called MDIO\_1P2\_SELECT\_N is provided that will force 1.2V operation on these signals, regardless of the VDD\_IO voltage.

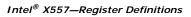

The management interface enables communication between the Station Management (STA) and a PHY. The STA is the external host controller which is the master of the management interface bus. Consequently, it always sources the MDC clock. When the MDIO is sourced by the STA, the PHY samples the MDIO at the rising edge of MDC. When the MDIO is sourced by the PHY during read operations, the STA samples the MDIO at the rising edge.

<sup>1.</sup> This is a function of whether the output is set to push-pull or open-drain mode, and on the capacitance of the bus.

### Table 2-1 X557-AT

| Signal Name     | Pin Name(s)                               | Pin<br>Number(s)                | Туре |                                                                                                                                                                                                                                                                                                                                              |

|-----------------|-------------------------------------------|---------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt*      | PO_INT_N                                  | K18                             | OD   | The 2.5V tolerant open-drain interrupt signal from PHY 0 of the X557. On reset this is set high. This input can be driven to operate at 1.2V via the MDIO_1P2_SELECT_N pin, regardless of the voltage on VDD_IO.<br>This open-drain 20 mA outputs are on the VDD_IO domain.                                                                  |

| MDIO<br>Address | ADDR0<br>ADDR1<br>ADDR2<br>ADDR3<br>ADDR4 | K15<br>J15<br>J16<br>H16<br>G17 | I    | The logic inputs to set the MDIO PHY address of the X557.<br>These inputs are on the VDD_IO domain and have pull-up<br>resistors associated with them.                                                                                                                                                                                       |

| MDIO Clock      | MDC                                       | J18                             | I/O  | The MDIO clock input for the X557.<br>This tri-state 20 mA I/O is on the VDD_IO domain.                                                                                                                                                                                                                                                      |

| MDIO Data       | MDIO                                      | L18                             | I/O  | The MDIO data line (with Schmitt triggered logic levels) for PHY<br>0 of the X557. On reset, this is set to high-impedance.<br>This tri-state 20 mA I/O is on the VDD_IO domain.                                                                                                                                                             |

| Reset Out*      | RST_OUT_N                                 | НЗ                              | OD   | The open-drain reset output from the X557. This might be used to drive the power-up reset signal for a board, as it outputs the on-chip power-up reset signal from the X557. This open-drain 20 mA output is on the VDD_IO domain.                                                                                                           |

| Reset*          | RST_N                                     | ]4                              | I    | The hard reset input (with Schmitt triggered logic levels) for<br>the X557. This input can be driven to operate at 1.2V via the<br>MDIO_1P2_SELECT_N pin, regardless of the voltage on<br>VDD_IO.<br>This input is on the VDD_IO domain and has a pull-up resistor<br>associated with it.                                                    |

| Tx Enable       | TX_EN                                     | F5                              | I    | When pulled low, this input disables the output line drivers on<br>the X557, and guarantees less than -53 dBm output power.<br>This input can be driven to operate at 1.2V via the<br>MDIO_1P2_SELECT_N pin, regardless of the voltage on<br>VDD_IO.<br>This input is on the VDD_IO domain and has a pull-up resistor<br>associated with it. |

### Table 2-2 X557-AT2

| Signal Name            | Pin Name(s)                      | Pin<br>Number(s)         | Туре |                                                                                                                                                                                                                                                                                                                                              |

|------------------------|----------------------------------|--------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved               | TX_DC_RST_N                      | H2                       | 0    | Reserved.                                                                                                                                                                                                                                                                                                                                    |

| Interrupt<br>[1:0]*    | P0_INT_N<br>P1_INT_N             | K18<br>K17               | OD   | The 2.5V tolerant open-drain interrupt signal from PHY 0 of the X557. On reset this is set high. This input can be driven to operate at 1.2V via the MDIO_1P2_SELECT_N pin, regardless of the voltage on VDD_IO.<br>These open-drain 20 mA outputs are on the VDD_IO domain.                                                                 |

| Invert MDIO<br>Address | INV_ADDR0                        | К15                      | I    | When set, these logic inputs invert the corresponding LSBs of<br>the MDIO PHY address of the X557 (XOR function).<br>This is used to change the counting order of the PHYs within<br>the X557.<br>This input is on the VDD_IO domain and has a pull-up resistor<br>associated with it.                                                       |

| MDIO<br>Address        | ADDR1<br>ADDR2<br>ADDR3<br>ADDR4 | J15<br>J16<br>H16<br>G17 | I    | The logic inputs to set the MDIO PHY address of the X557.<br>These inputs are on the VDD_IO domain and have pull-up<br>resistors associated with them.                                                                                                                                                                                       |

| MDIO Clock<br>[1:0]    | P0_MDC<br>P1_MDC                 | J18<br>J17               | I/O  | The MDIO clock input for PHY 0 of the X557. This input can be driven to operate at 1.2V via the MDIO_1P2_SELECT_N pin, regardless of the voltage on VDD_IO.<br>These tri-state 20 mA I/Os are on the VDD_IO domain.                                                                                                                          |

| MDIO Data<br>[1:0]     | P0_MDIO<br>P1_MDIO               | L18<br>L17               | I/O  | The MDIO data line (with Schmitt triggered logic levels) for PHY<br>0 of the X557. On reset, this is set to high-impedance. This I/O<br>can be driven to operate at 1.2V via the MDIO_1P2_SELECT_N<br>pin, regardless of the voltage on VDD_IO.<br>These tri-state 20 mA I/Os are on the VDD_IO domain.                                      |

| Reset Out*             | RST_OUT_N                        | Н3                       | OD   | The open-drain reset output from the X557. This might be used<br>to drive the power-up reset signal for a board, as it outputs the<br>on-chip power-up reset signal from the X557.<br>This open-drain 20 mA output is on the VDD_IO domain.                                                                                                  |

| Reset*                 | RST_N                            | ]4                       | I    | The hard reset input (with Schmitt triggered logic levels) for<br>the X557. This input can be driven to operate at 1.2V via the<br>MDIO_1P2_SELECT_N pin, regardless of the voltage on<br>VDD_IO.<br>This input is on the VDD_IO domain and has a pull-up resistor<br>associated with it.                                                    |

| Tx Enable              | TX_EN                            | F5                       | I    | When pulled low, this input disables the output line drivers on<br>the X557, and guarantees less than -53 dBm output power.<br>This input can be driven to operate at 1.2V via the<br>MDIO_1P2_SELECT_N pin, regardless of the voltage on<br>VDD_IO.<br>This input is on the VDD_IO domain and has a pull-up resistor<br>associated with it. |

Table 2-3 shows the management interface frame format (802.3-2005 45.3). The fields are described in the sections that follow.

| Frame                             | PRE | ST | OP | PHYAD | MMDAD | ТА | Data            | Idle |

|-----------------------------------|-----|----|----|-------|-------|----|-----------------|------|

| Address                           | 11  | 00 | 00 | PPPPP | EEEEE | 10 | ААААААААААААА   | Z    |

| Write                             | 11  | 00 | 01 | РРРРР | EEEEE | 10 | DDDDDDDDDDDDDD  | Z    |

| Read                              | 11  | 00 | 11 | РРРРР | EEEEE | Z0 | DDDDDDDDDDDDDD  | Z    |

| Post-read<br>increment<br>address | 11  | 00 | 10 | РРРРР | EEEEE | Z0 | DDDDDDDDDDDDDDD | Z    |

#### Table 2-3 MDIO Frame Format

#### Idle (idle condition):

The idle condition on the management interface is a high-impedance state. All tri-state drivers are disabled and the pull-up resistor(s) on the MDIO bus will pull the MDIO line to a one.

#### PRE (preamble):

Normal operation — At the beginning of each transaction, the station management entity will send a sequence of 32 contiguous ones on the MDIO data line, along with 32 corresponding cycles on the MDC to provide the MMD with a pattern that it can use to establish synchronization. Each MMD will observe a sequence of 32 contiguous one bits on MDIO with 32 corresponding cycles on MDC before it responds to any transaction.

Preamble suppression — The MDIO interface can optionally disable preamble detection by setting the *MDIO Preamble Detection Disable* bit in the Global General Provisioning 2: Address 1E.C441 register. In this mode of operation, one or more preamble bit are required followed by the 0x0 start of frame ST bits.

#### ST (start of frame):

The start of frame for indirect access cycles is indicated by the <00> pattern. This pattern assures a transition from the default one and identifies the frame as an indirect access. Frames that contain the ST=<01> pattern defined in Clause 22 will be ignored by the MMDs within the X557.

#### **OP (operation code):**

The operation code field indicates the type of transaction being performed by the frame. A <00> pattern indicates that the frame payload contains the address of the register to access. A <01> pattern indicates that the frame payload contains data to be written to the register whose address was provided in the previous address frame. A <11> pattern indicates that the frame is read operation. A <10> pattern indicates that the frame is a post-read increment address operation.

#### PHYAD (PHY address):

The PHY address is five bits, allowing for 32 unique PHY addresses, and hence up to 32 PHYs on an MDIO bus. The address of the PHY is determined from ADDR[4:0] for the X557-AT and ADDR[4:1] for the X557-AT2 pins. The first PHY address bit to be transmitted and received is the MSB of the address. The station management entity must have a priori knowledge of the appropriate PHY address for each PHY to which it is attached, whether connected to a single PHY or to multiple PHYs.

#### MMDAD (MMD address):

The MMD address is five bits, allowing for 32 unique MMDs per PHY. The first MMD address bit transmitted and received is the MSB of the address.

In addition the X557 supports a broadcast mode when the PHYAD is 0x00. Only the write and load address opcodes are supported in broadcast mode. Read and post-read increment opcodes are ignored in broadcast mode. This mode of operation can be enabled via the *MDIO Broadcast Mode Enable* bits in the Global General Provisioning 2: Address 1E.C441 register.

#### TA (turnaround):

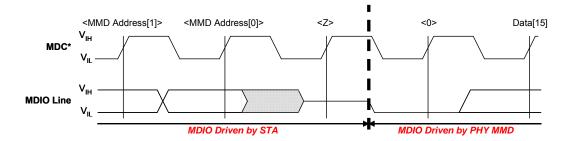

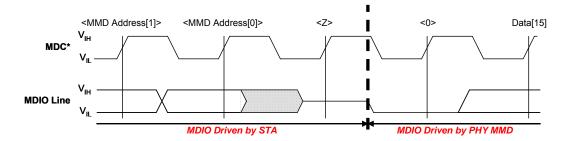

The turnaround time is a 2-bit time spacing between the MMD address field and the data field of a management frame to avoid contention during a read transaction. For a read or post-read increment address transaction, both the STA and the MMD remain in a high-impedance state for the first bit time of the turnaround. The MMD then drives a zero bit during the second bit time of the turnaround of a read or post-read increment address transaction. During a write or address transaction, the STA transmits a one for the first bit time of the turnaround and a zero for the second bit time of the turnaround. This behavior is shown in

#### Figure 2-1 MDIO Bus Turn-around During Read Operations

#### Address / Data:

The address/data field is 16 bits. For an address cycle, it contains the address of the register to be accessed on the next cycle. For the data cycle of a write frame, the field contains the data to be written to the register. For a read or post-read increment address frame, the field contains the contents of the register. The first bit transmitted and received shall be bit 15.

For counters that are greater than 16-bits, the LSW must be read first, then the MSW must be read immediately afterwards. When the LSW is read, the counter is cleared and the MSW is stored in a shadow register. Reading the MSW actually reads the shadow register.

Optionally the host may read the MSW first, then the LSW immediately afterwards by setting the *MDIO Read MSW First Enable* bit in the Global General Provisioning 2: Address 1E.C441 register.

### 2.1.1 Interrupt

The X557 supports an open-drain interrupt pin per PHY.

### 2.1.2 Reset

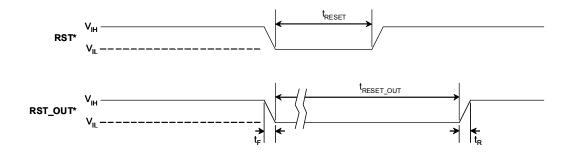

The X557 is capable of generating a RST\_OUT\_N signal from its internal power-on reset generation circuitry that can be used by the external board circuitry.

Operation of the reset machinery is as follows:

1. Release from the Reset state begins when the RST\_N input is high<sup>1</sup>, and all of the core power supplies are above their required thresholds. These thresholds are listed in

### Table 2-4 Power-on Reset Thresholds for Core Supply Voltages

| Supply | Parameter                                      | Min  | Мах  | Units |

|--------|------------------------------------------------|------|------|-------|

| VCC2P1 | Power-on reset threshold for VCC2P1 DC supply. | 1.70 | 1.80 | V     |

| VCC1P2 | Power-on reset threshold for VCC1P2 DC supply. | 0.93 | 0.99 | V     |

| VDD    | Power-on reset threshold for VDD DC supply.    | 0.56 | 0.60 | V     |

- 2. Once all of the conditions for release from reset are true, a 20 ms timer engages, the purpose of which is to enable the supplies to settle prior to allowing the PHY to boot.

- 3. After the 20 ms timer has completed, hardware state machines designed to guarantee PLL and band-gap stability engage.

- 4. After the PLLs and band-gap are locked and functioning properly, the processor and digital circuitry are released from reset.

- 5. The PHY image is then loaded and the processor boots.

- 6. After the processor boots, any provisioned register values are set, and the PHY enters the provisioned operating state.

- 7. Once this completes, the processor raises the MMD reset bits and sets the reset completed alarm, indicating it has completed reset and is ready for operation.

### 2.1.3 Configuration

The X557 contains a number of static configuration pins which are used to set the power-up operation of the X557. These signals are:

- 1. MDIO address ADDR[4:0] for the X557-AT and ADDR[4:1] for the X557-AT2.

- 2. Transmit Enable

<sup>1.</sup> Note that there are no timing requirements on issuance of reset relative to the clock.

In the X557-AT2 package, the MDIO addressing is tied off internally so that the LSB increments according to the PHY number in the package. This MDIO address can either be overridden via a register in the Global MMD via provisioning, or the incrementation order can be altered via the INV\_ADDR0 pin which is exclusive OR'd with address pin ADDR0.

# 2.2 Serial Flash

### 2.2.1 SPI Flash Interface

| Signal Name               | Pin Name(s) | Pin<br>Number(s) | Туре |                                                                                                                                                  |

|---------------------------|-------------|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved                  | RX_DC_CLK   | J1               | Ι    | Reserved                                                                                                                                         |

| Reserved                  | TX_DC_CLK   | N18              | 0    | Reserved                                                                                                                                         |

| Reserved                  | RX_DC_DATA  | H1               | I    | Reserved                                                                                                                                         |

| Reserved                  | TX_DC_DATA  | M17              | 0    | Reserved                                                                                                                                         |

| Reserved                  | DC_MASTER_N | E1               | Ι    | Reserved                                                                                                                                         |

| Reserved                  | RX_DC_RST_N | N17              | Ι    | Reserved                                                                                                                                         |

| Reserved                  | TX_DC_RST_N | H2               | 0    | Reserved                                                                                                                                         |

| Reserved                  | RX_DC_SOF   | 32               | I    | Reserved                                                                                                                                         |

| Reserved                  | TX_DC_SOF   | M18              | 0    | Reserved                                                                                                                                         |

| SPI Chip<br>Enable        | CE_N        | G2               | 0    | The SPI CE* signal from the X557 to the serial Flash.<br>On reset this is set high.<br>This 20 mA output is on the VDD_FLASH domain.             |

| SPI Serial<br>Clock       | SCLK        | G1               | 0    | The SPI clock from the X557 to the serial Flash. On reset this is set low.<br>This 20 mA output is on the VDD_FLASH domain.                      |

| SPI Serial<br>Input Data  | SIN         | F1               | I    | The SPI input data from the serial FLASH to the X557.<br>This input is on the VDD_FLASH domain and has a pull-up<br>resistor associated with it. |

| SPI Serial<br>Output Data | SOUT        | F2               | I    | The SPI output data from the X557 to the serial Flash.<br>On reset this is set low.<br>This 20 mA output is on the VDD_FLASH domain.             |

The SPI interface is responsible for connecting the X557 to the external Flash memory device. The micro-controller on the X557 accesses the boot code and the X557 default register values from the Flash memory after power-on reset. This Flash memory is also accessible via the MDIO interface for firmware updates and manufacturing burn via the registers in the Global MMD.

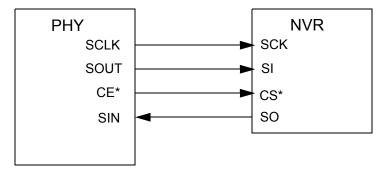

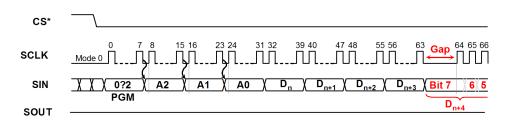

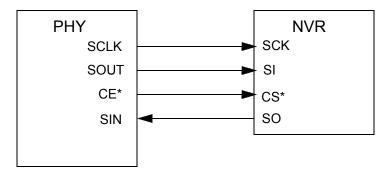

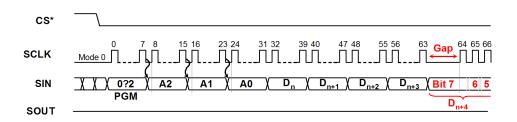

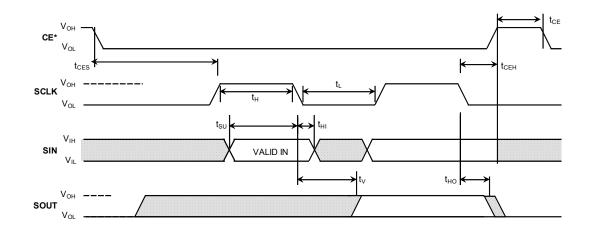

The SPI interface is a four wire, unidirectional, serial bus as shown in Figure 2-2. It is composed of a serial clock output SCLK, a serial data output SOUT, a serial data input SIN, and a chip-select CE\*. All the signals are unidirectional.

### Figure 2-2 SPI Interface Block Diagram

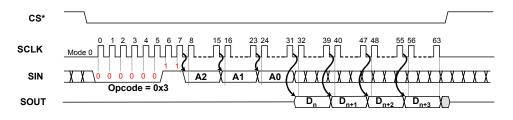

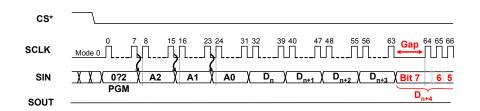

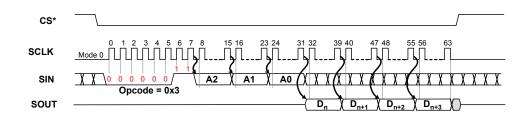

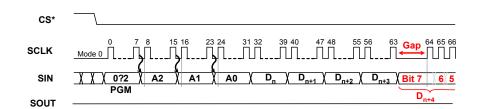

The X557 is set up to function as a Mode 0 (0,0) SPI device, which means that the clock defaults to zero when not bursting. Data on this interface, for both SIN and SOUT, is always sourced on the falling edge of SCLK, and sampled on the rising edge of SCLK.

The following figures show typical read, burst read, and write operations for the X557. In all of these scenarios, the Non-volatile RAM (NVR) interface in the Global MMD is used to access the Flash.

Note: NVR used throughout this document is synonymous with Non-volatile Memory (NVM).

The NVR interface in the X557 is designed to be able to output any arbitrary opcode, followed by a programmable zero to three address bytes, followed by a programmable zero to four data bytes. This allows any variation of opcodes to be output to the attached Flash device. This interface also supports a burst read and write mode, which keeps the CS\* line pulled low to enable back-to-back reads and writes. To support this, the NVR interface supports two 16-bit address registers and two 16-bit data registers, which allows up to 4 data bytes in a burst over the SPI interface. In order to extend this to longer bursts, the X557 halts the clock after the last bit in the data burst allowing the host processor to load another block of data to / from the NVR interface. This is shown in Figure 2-3 through Figure 2-5 and enables the data burst to be extended by as many bytes as necessary, without outstripping the MDIO's I/O capabilities.

Note that typical NVRs require that writing be performed on a block basis, and thus the addresses usually wrap within the block being programmed. As such, it is desirable from a speed and efficiency perspective to attempt to write entire blocks, versus pieces of blocks.

In order to assure that no polling is required on NVR interface, it is recommended that the NVR clock speed be set to at least<sup>1</sup>:

$$f_{\rm SCLK} > \frac{64}{63} \cdot f_{\rm MDIO}$$

The desired Flash memory should be chosen to be at least 512K bytes in size, and must be capable of interfacing to a 2.5V CMOS SPI.

### 2.3 Firmware

The X557 contains a 32-bit micro-controller. This micro-controller is designed to have it's IRAM and DRAM either loaded on power-up / reset from the attached FLASH or to have its boot image loaded by the host processor via the MDIO interface.

<sup>1.</sup> This is derived from the fact that the longest burst instruction on the SPI is 64 bits, at one bit per clock, whereas to write a register on the MDIO takes 64 clocks, and the data is not written until the last bit - hence the 63.

Hardware Interfaces (X557-AT and X557-AT2)—Intel® X557-AT/AT2/AT4 10 GbE PHY Datasheet

# 2.4 SerDes

### Table 2-5 X557-AT

| Signal Name | Pin Name(s)                | Pin<br>Number(s) | Туре | Description                                                                                                       |

|-------------|----------------------------|------------------|------|-------------------------------------------------------------------------------------------------------------------|

| Lane 0 Rx   | P0_RX_LN0_P<br>P0_RX_LN0_N | P2<br>P1         | I    | Physical Lane 0 differential Rx of the X557 SerDes interface.<br>This lane can operate in KR, XFI and SGMII mode  |

| Lane 0 Tx   | P0_TX_LN0_P<br>P0_TX_LN0_N | T2<br>T1         | 0    | Physical Lane 0 differential Tx of the X557 SerDes interface.<br>This lane can operate in KR, XFI and SGMII mode. |

| Lane 1 Rx   | P0_RX_LN1_P<br>P0_RX_LN1_N | U2<br>V2         | I    | Physical Lane 1 differential Rx of the X557 SerDes interface.<br>This lane can operate in SGMII mode              |

| Lane 1 Tx   | P0_TX_LN1_P<br>P0_TX_LN1_N | U3<br>V3         | 0    | Physical Lane 1 differential Tx of the X557 SerDes interface.<br>This lane can operate in SGMII mode.             |

| Lane 2 Rx   | P0_RX_LN2_P<br>P0_RX_LN2_N | U4<br>V4         | I    | Physical Lane 2 differential Rx of the X557 SerDes interface.<br>This lane can operate in KR, XFI and SGMII mode  |

| Lane 2 Tx   | P0_TX_LN2_P<br>P0_TX_LN2_N | U6<br>V6         | 0    | Physical Lane 2 differential Tx of the X557 SerDes interface.<br>This lane can operate in KR, XFI and SGMII mode. |

| Lane 3 Rx   | P0_RX_LN3_P<br>P0_RX_LN3_N | U7<br>V7         | I    | Physical Lane 3 differential Rx of the X557 SerDes interface.<br>This lane can operate in SGMII mode.             |

| Lane 3 Tx   | P0_TX_LN3_P<br>P0_TX_LN3_N | U8<br>V8,        | 0    | Physical Lane 3 differential Tx of the X557 SerDes interface.<br>This lane can operate in SGMII mode.             |

#### Table 2-6 X557-AT2

| Signal Name | Pin Name(s)                                              | Pin<br>Number(s)       | Туре | Description                                                                                                       |

|-------------|----------------------------------------------------------|------------------------|------|-------------------------------------------------------------------------------------------------------------------|

| Lane 0 Rx   | P0_RX_LN0_P<br>P0_RX_LN0_N<br>P1_RX_LN0_P<br>P1_RX_LN0_N | P2<br>P1<br>U10<br>V10 | I    | Physical Lane 0 differential Rx of the X557 SerDes interface.<br>This lane can operate in KR, XFI and SGMII mode. |

| Lane 0 Tx   | P0_TX_LN0_P<br>P0_TX_LN0_N<br>P1_TX_LN0_P<br>P1_TX_LN0_N | T2<br>T1<br>U12<br>V12 | 0    | Physical Lane 0 differential Tx of the X557 SerDes interface.<br>This lane can operate in KR, XFI and SGMII mode. |

| Signal Name | Pin Name(s)                                              | Pin<br>Number(s)       | Туре | Description                                                                                                       |

|-------------|----------------------------------------------------------|------------------------|------|-------------------------------------------------------------------------------------------------------------------|

| Lane 1 Rx   | P0_RX_LN1_P<br>P0_RX_LN1_N<br>P1_RX_LN1_P<br>P1_RX_LN1_N | U2<br>V2<br>U13<br>V13 | I    | Physical Lane 1 differential Rx of the X557 SerDes interface.<br>This lane can operate in SGMII mode.             |

| Lane 1 Tx   | P0_TX_LN1_P<br>P0_TX_LN1_N<br>P1_TX_LN1_P<br>P1_TX_LN1_N | U3<br>V3<br>U14<br>V14 | 0    | Physical Lane 1 differential Tx of the X557 SerDes interface.<br>This lane can operate in SGMII mode.             |

| Lane 2 Rx   | P0_RX_LN2_P<br>P0_RX_LN2_N<br>P1_RX_LN2_P<br>P1_RX_LN2_N | U4<br>V4<br>U15<br>V15 | I    | Physical Lane 2 differential Rx of the X557 SerDes interface.<br>This lane can operate in KR, XFI and SGMII mode  |

| Lane 2 Tx   | P0_TX_LN2_P<br>P0_TX_LN2_N<br>P1_TX_LN2_P<br>P1_TX_LN2_N | U6<br>V6<br>U17<br>V17 | 0    | Physical Lane 2 differential Tx of the X557 SerDes interface.<br>This lane can operate in KR, XFI and SGMII mode. |

| Lane 3 Rx   | P0_RX_LN3_P<br>P0_RX_LN3_N<br>P1_RX_LN3_P<br>P1_RX_LN3_N | U7, V7,<br>T17,<br>T18 | I    | Physical Lane 3 differential Rx of the X557 SerDes interface.<br>This lane can operate in SGMII mode              |

| Lane 3 Tx   | P0_TX_LN3_P<br>P0_TX_LN3_N<br>P1_TX_LN3_P<br>P1_TX_LN3_N | U8, V8,<br>R17,<br>R18 | 0    | Physical Lane 3 differential Tx of the X557 SerDes interface.<br>This lane can operate in SGMII mode.             |

The X557 SerDes interface is both robust and flexible and provides numerous loopback and diagnostic capabilities that eases system interface-PHY board design and bring up as well as AC JTAG. The interface is capable of providing arbitrary lane swapping and inversion. In the transmit direction, there is a programmable 4-tap equalizer (1 pre-cursor, and 2 post-cursor taps) as well as the ability to program the Tx drive strength and Tx termination. In the receive direction, there is programmable gain and programmable boost.

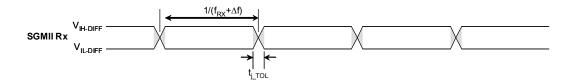

In SGMII mode, the interface operates at 1.25 Gb/s over SerDes logical Lane 0 and is compliant to the Cisco\* SGMII specification[10]. In KR mode, one 10 GbE interface is provided operating over Lane 2.

The SerDes interface on the X557 also contains diagnostic pattern generation and checking functionality listed Table 2-7:

### Table 2-7 KR Diagnostic Pattern Capabilities

| Test                 | Description           | Generate | Check | Invert |

|----------------------|-----------------------|----------|-------|--------|

| x <sup>9</sup> PRBS  | $x^9 + x^5 + 1$       | 3        | 3     | 3      |

| x <sup>31</sup> PRBS | $x^{31} + x^{28} + 1$ | 3        | 3     | 3      |

| Test         | Description           | Generate | Check | Invert |

|--------------|-----------------------|----------|-------|--------|

| Square Wave  | Clause 49.2.12        | 3        | 3     | 3      |

| Pseudo-Noise | Clause 49.2.12        | 3        | 3     | 3      |

| CRPAT        | IEEE 802.3 Annex48A.4 | 3        | 3     | 3      |

### Table 2-8 SGMII Diagnostic Pattern Capabilities

| Test  | Description           | Generate | Check | Invert |

|-------|-----------------------|----------|-------|--------|

| CRPAT | IEEE 802.3 Annex48A.4 | 3        | 3     | 3      |

All of the parameters associated with the SerDes interface have provisionable default values, which means that the X557 SerDes interface can be tailored to power-up with the optimal settings for any given application.

# 2.5 SerDes Operating Modes

For the purposes of this discussion, the X557 can be viewed as a set of blocks as shown below:

On the left side of the diagram is the system interface, which consists of the four SerDes lanes. Lanes 0 and 2 have the ability to run at rates from 1.25 Gb/s to 10.3125 Gb/s. These lanes support SGMII and KR. The other two lanes only support 1.25 Gb/s and 3.125 Gb/s rates (SGMII). At the PCS layer, there are two SGMII cores and two KR cores.

#### Figure 2-6 X557-AT/AT2 Operational Blocks

These different SerDes operating modes are summarized in Table 2-9.

#### Table 2-9 SerDes Lane Assignments for Different Operating Modes

| Interface | Operating Mode /<br>Core Used | Lane 0 | Lane 1   | Lane 2 | Lane 3 |   |   |

|-----------|-------------------------------|--------|----------|--------|--------|---|---|

| System    | SGMII1                        |        | SGMII1 X |        | х      | х | Х |

| System    | KR1                           |        |          | х      |        |   |   |

### 2.6 SerDes System I/F Startup

In startup on the system interface side, there are three different operating scenarios for the SerDes I/F:

- 10 GbE mode (KR or XFI)

- 1000BASE-X mode

- SGMII

- All-off mode

These different modes affect only the system interface and function independently of whether the MDI interface is selected or not.

### 2.6.1 **10 GbE Mode**

- 1. In this mode, which is the hardware default, the X557 comes up in the pre-configured 10 GbE mode (KR/XFI) and transmits Local Faults / Idles, and remains in this state until a connection to a link partner is established.

- After connection to a link partner has been established, the X557 will either stay in the preconfigured 10 GbE mode, or switch to 1000BASE-X mode on logical Lane 0, or 100 Mb/s SGMII mode depending on that the auto-negotiated line rate was.

- 3. Once the SerDes I/F has synchronized, traffic flows.

- a. If the link fails and the system interface was in 10 GbE mode, the X557 generates a Local Fault message towards the system I/F, effectively restarting. If the link had transitioned to 1 GbE operation, the SerDes is restarted in 10 GbE mode generating Local Faults / Idles.

- 4. Auto-negotiation restarts after the link break timer expires.

### 2.6.2 1000BASE-X Mode

- 1. In this mode the X557 comes up in 1000BASE-X mode on logical Lane 0 and transmits idles, and remains in this state until a connection to a link partner is established.

- 2. After a connection to a link partner has been established, the X557 will either stay in 1000BASE-X mode, or switch to the pre-configured 10 GbE mode, or 100 Mb/s SGMII mode depending on that the auto-negotiated line rate was.

Hardware Interfaces (X557-AT and X557-AT2)—Intel<sup>®</sup> X557-AT/AT2/AT4 10 GbE PHY Datasheet

- 3. Once the SerDes I/F has synchronized, traffic flows.

- 4. If the link fails and the system interface was in the pre-configured 10 GbE mode (KR/XFI), the X557 generates a Local Fault message towards the system I/F, and effectively restarts in 1000BASE-X mode, generating Idles. Otherwise the link just stays in 1000BASE-X mode generating Idles.

- 5. Auto-negotiation restarts after the link break timer expires.

### 2.6.3 SGMI1 Mode

- 1. In this mode, the X557 comes up in SGMII mode. After sending and receiving an ACK on an SGMII link-down, auto-negotiation message (see Table 2-11), the SerDes transmits idles and remains in this state until a link partner connection is established.

- 2. After a connection to a link partner has been established, the X557 sends an SGMII link-up, autonegotiation message with the appropriate rate (see Table 2-11) and receives an ACK.

- 3. Upon receiving the acknowledge from the system interface, the X557 either switches to 100 Mb/s SGMII mode, stays in 1 GbE SGMII mode (essentially 1000BASE-X) or switches to the preconfigured 10 GbE mode (KR or XFI), depending on whether the auto-negotiated line rate was 1 GbE / 100 Mb/s or 10 GbE.

- 4. Once the SerDes interface has synchronized, traffic flows.

- 5. If the link fails and the X557 was in the pre-configured 10 GbE mode, the X557 generates a local fault message towards the system interface and then transitions back to SGMII mode, where it sends and receives an ACK on an SGMII link-down, auto-negotiation message and then resumes transmitting idles. If the link fails and the X557 was in 1 GbE SGMII mode, the X557 first sends and receives an ACK on an SGMII link-down, auto-negotiation message and then resumes transmitting idles with no interruption in SerDes operation. If the system interface was in 100 Mb/s SGMII mode, the SerDes transitions back to SGMII mode, where it sends and receives an ACK on an SGMII mode, the SerDes transitions back to SGMII mode, where it sends and receives an ACK on an SGMII link-down, auto-negotiation message and then resumes transmitting idles.

- 6. Auto-negotiation restarts after the link break timer expires.

### 2.6.4 All-Off Mode

- 1. In this mode the Intel® X557-AT/AT2/AT4 10 GbE PHY comes up with the system interface off, and remains in this state until connection to a link partner is established.

- 2. After connection to a link partner has been established, the Intel® X557-AT/AT2/AT4 10 GbE PHY will either turn on 1000BASE-X on logical Lane 0, or turn on the pre-configured 10 GbE mode (KR), or 100 Mb/s SGMII mode depending on that the auto-negotiated line rate was.

- 3. Once the SerDes I/F has synchronized, traffic flows.

- 4. If the link fails and was in the pre-configured 10 GbE mode, the Intel® X557-AT/AT2/AT4 10 GbE PHY generates a Local Fault message towards the system I/F and shuts off. Otherwise the system interface just shuts off.

- 5. Auto-negotiation restarts after the link break timer expires.

### 2.6.5 Interrupts

In all of these modes, the processor has the ability to generate an interrupt upon completing autonegotiation.

# 2.7 MDI

| Signal Name  | Pin Name(s)        | Pin<br>Number(s) | Туре | Description                                                                                                                                                                                  |

|--------------|--------------------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHY 0 CMS    | P0_CM_P<br>P0_CM_N | E8<br>D8         | I/O  | PHY 0 Common Mode Sense Input.                                                                                                                                                               |

| PHY 0 Pair A | P0_A_P<br>P0_A_N   | B2<br>A2         | I/O  | PHY 0 Pair A of the X557 line interface. These should connect to the Pair A inputs of the transformer, with capacitive bypassing via the center-tap. On reset this is set to high-impedance. |

| PHY 0 Pair B | P0_B_P<br>P0_B_N   | B4<br>A4         | I/O  | PHY 0 Pair B of the X557 line interface. These should connect to the Pair B inputs of the transformer, with capacitive bypassing via the center-tap. On reset this is set to high-impedance. |

| PHY 0 Pair C | P0_C_P<br>P0_C_N   | B6<br>A6         | I/O  | PHY 0 Pair C of the X557 line interface. These should connect to the Pair C inputs of the transformer, with capacitive bypassing via the center-tap. On reset this is set to high-impedance. |

| PHY 0 Pair D | P0_D_P<br>P0_D_N   | B8<br>A8         | I/O  | PHY 0 Pair D of the X557 line interface. These should connect to the Pair D inputs of the transformer, with capacitive bypassing via the center-tap. On reset this is set to high-impedance. |

### Table 2-10 X557-AT2

| Signal Name  | Pin Name(s)        | Pin<br>Number(s) | Туре | Description                                                                                                                                                                                  |

|--------------|--------------------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHY 1 CMS    | P1_CM_P<br>P1_CM_N | C18<br>B18       | I/O  | PHY 1 Common Mode Sense Input.                                                                                                                                                               |

| PHY 1 Pair A | P1_A_P<br>P1_A_N   | B11<br>A11       | I/O  | PHY 1 Pair A of the X557 line interface. These should connect to the Pair A inputs of the transformer, with capacitive bypassing via the center-tap. On reset this is set to high-impedance. |

| PHY 1 Pair B | P1_B_P<br>P1_B_N   | B13<br>A13       | I/O  | PHY 1 Pair B of the X557 line interface. These should connect to the Pair B inputs of the transformer, with capacitive bypassing via the center-tap. On reset this is set to high-impedance. |

| PHY 1 Pair C | P1_C_P<br>P1_C_N   | B15<br>A15       | I/O  | PHY 1 Pair C of the X557 line interface. These should connect to the Pair C inputs of the transformer, with capacitive bypassing via the center-tap. On reset this is set to high-impedance. |

| PHY 1 Pair D | P1_D_P<br>P1_D_N   | B17<br>A17       | I/O  | PHY 1 Pair D of the X557 line interface. These should connect to the Pair D inputs of the transformer, with capacitive bypassing via the center-tap. On reset this is set to high-impedance. |

### Table 2-11 X557-AT

| Signal Name | Pin Name(s)  | Pin<br>Number(s) | Туре | Description                                                                                                                                                                            |

|-------------|--------------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMS         | CM_P<br>CM_N | E8<br>D8         | I/O  | Common Mode Sense Input.                                                                                                                                                               |

| Pair A      | A_P<br>A_N   | B2<br>A2         | I/O  | Pair A of the X557 line interface. These should connect to the Pair A inputs of the transformer, with capacitive bypassing via the center-tap. On reset this is set to high-impedance. |

| Pair B      | B_P<br>B_N   | B4<br>A4         | I/O  | Pair B of the X557 line interface. These should connect to the Pair B inputs of the transformer, with capacitive bypassing via the center-tap. On reset this is set to high-impedance. |

| Pair C      | C_P<br>C_N   | B6<br>A6         | I/O  | Pair C of the X557 line interface. These should connect to the Pair C inputs of the transformer, with capacitive bypassing via the center-tap. On reset this is set to high-impedance. |

| Pair D      | D_P<br>D_N   | B8<br>A8         | I/O  | Pair D of the X557 line interface. These should connect to the Pair D inputs of the transformer, with capacitive bypassing via the center-tap. On reset this is set to high-impedance. |

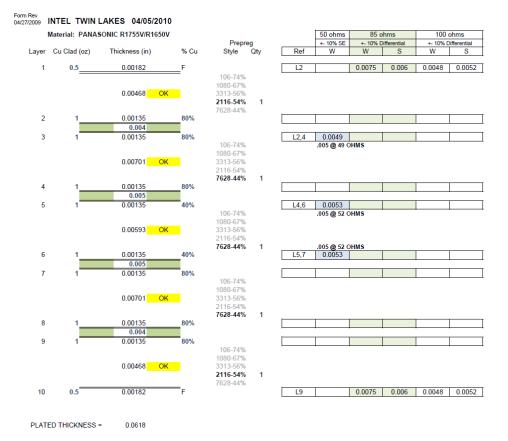

In 10 GbE mode, the line interface on the Intel® X557-AT/AT2/AT4 10 GbE PHY is capable of driving up to 100 m of CAT-6a unshielded twisted pair or 100 m of CAT-7 shielded cable (100  $\Omega$  differential impedance). It can also drive 55 m of CAT-6 cable, and a lesser distance of CAT-5e cable<sup>1</sup>. In 1 GbE and 100 Mb/s modes, it can drive 130m of CAT-5e (or better) cable. It is designed to drive this via a quad, 50  $\Omega$ , center-tapped 1:1 transformer connected to an RJ-45 PCB-mount jack.

<sup>1.</sup> This distance is indeterminate because CAT-5e cable performance is not specified past 100 MHz.

The line interface on the Intel® X557-AT/AT2/AT4 10 GbE PHY supports automatic A/B and C/D pair swaps, inversions (auto-X), and semi-cross (A/B or C/D only). It also supports a provisioned ABCD to DCBA pair reversal for ease of routing with stack-jacks via bit 1.E400.0 and the MDI\_CFG pin, which sets the configuration on power-up. Note that this reversal does not swap polarities, thus A+ maps to D+, etc.

# 2.8 Timing

The Intel® X557-AT/AT2/AT4 10 GbE PHY contains a high-performance synthesizer, which is capable of producing all of the clocks required internally, as well as sourcing the recovered 50 MHz CMOS clock for use by other components in the system. This synthesizer operates from either an external 100  $\mu$ W 50.000 MHz crystal (future X557-AT) or from a differential 50 MHz clock.

Note: Either a 50 MHZ crystal or a 50 MHz oscillator can be implemented with the X557-AT (single port) device (crystal mode or oscillator mode, XTAL\_SELECT\_N = 0b or XTAL\_SELECT\_N = 1b). However, a 50 MHZ oscillator must be implemented for use with the X557-AT2 (dual port) and X557-AT4 (quad port) devices (LVDS oscillator mode, XTAL\_SELECT\_N = 1b).

Table 2-12 X557-AT2

| Signal Name | Pin Name(s)      | Pin<br>Number(s) | Туре | Description                                                                                                                                                  |

|-------------|------------------|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Input | CLK_P<br>CLK_N   | F18<br>G18       | I    | The 50 MHz differential LVDS reference clock input for the X557. This DC-coupled input has an internal 100 $\Omega$ termination resistor associated with it. |

| Reserved    | RNC_N15          | N15              | Ι    | Reserved                                                                                                                                                     |

| Reserved    | RNC_D1<br>RNC_C1 | D1<br>C1         | I    | Reserved                                                                                                                                                     |

| Reserved    | RNC_D2           | D2               | 0    | Reserved                                                                                                                                                     |

| Reserved    | RNC_E2           | E2               | 0    | Reserved                                                                                                                                                     |

#### Table 2-13 X557-AT

| Signal Name                 | Pin Name(s)      | Pin<br>Number(s) | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------|------------------|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Crystal Input<br>(future)   | XTAL_I           | F18              | I    | The 50 MHz reference clock input for the X557. When XTAL_SELECT_N is pulled low, these pins operate in crystal mode, otherwise they are the differential LVDS inputs for an external oscillator, with XTAL_I being the positive input and XTAL_O being the negative input. In oscillator mode, this DC-coupled input has an internal 100 $\Omega$ termination resistor associated with it. |

| Crystal Output<br>(future)  | XTAL_O           | G18              | I    | The 50 MHz crystal oscillator output of the X557. This connects to the output of an inverting amplifier. In XO mode, this is high-impedance.                                                                                                                                                                                                                                               |

| Reserved                    | RNC_N15          | N15              | Ι    | Reserved                                                                                                                                                                                                                                                                                                                                                                                   |

| Reserved                    | RNC_D1<br>RNC_C1 | D1<br>C1         | Ι    | Reserved                                                                                                                                                                                                                                                                                                                                                                                   |

| Reserved                    | RNC_D2           | D2               | 0    | Reserved                                                                                                                                                                                                                                                                                                                                                                                   |

| 50 MHz Clock<br>Termination | 50M_CLK_TERM     | G13              | I    | Selects whether PHY provides $100 \Omega$ differential termination for<br>a 50 MHz clock input:<br>1b = Terminated.<br>0b = Open.<br>This input is on the VDD_IO domain and has a pull-up resistor<br>associated with it.                                                                                                                                                                  |

| Clock Source<br>Select*     | XTAL_SELECT_N    | F17              | I    | The 50 MHz reference clock source selector for the X557-AT.<br>When XTAL_SELECT_N is pulled low, these XTAL_I and XTAL_O<br>pins operate in crystal mode; otherwise, they operate in LVDS<br>oscillator input mode.<br>This input is on the VDD_IO domain and has a pull-up resistor<br>associated with it.                                                                                |

# 2.9 LED

The X557 supports three 20 mA open-drain CMOS LED outputs.

### Table 2-14 X557-AT2

| Signal Name        | Pin Name(s)                   | Pin<br>Number(s) | Туре | Description                                                                                                      |

|--------------------|-------------------------------|------------------|------|------------------------------------------------------------------------------------------------------------------|

| PHY 0 LED<br>[2:0] | P0_LED0<br>P0_LED1<br>P0_LED2 | K1<br>L1<br>M1   | OD   | The 2.5V tolerant, open-drain LED outputs for PHY 0.<br>These open-drain 20 mA outputs are on the VDD_IO domain. |

| PHY 1 LED<br>[2:0] | P1_LED0<br>P1_LED1<br>P1_LED2 | K2<br>L2<br>M2   | OD   | The 2.5V tolerant, open-drain LED outputs for PHY 1.<br>These open-drain 20 mA outputs are on the VDD_IO domain. |

### Table 2-15 X557-AT

| Signal Name | Pin Name(s)          | Pin<br>Number(s) | Туре | Description                                                                                                        |

|-------------|----------------------|------------------|------|--------------------------------------------------------------------------------------------------------------------|

| LED [2:0]   | LED0<br>LED1<br>LED2 | K1<br>L1<br>M1   | OD   | The 2.5V tolerant, open-drain LED outputs for the PHY.<br>These open-drain 20 mA outputs are on the VDD_IO domain. |

Hardware Interfaces (X557-AT and X557-AT2)—Intel<sup>®</sup> X557-AT/AT2/AT4 10 GbE PHY Datasheet

# 2.10 Reference Resistors

The X557 relies on 1% precision resistors to calibrate its internal voltage levels.

Table 2-16 X557-AT2

| Signal Name                      | Pin Name(s)          | Pin<br>Number(s) | Туре   | Description                                                                                                                           |

|----------------------------------|----------------------|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| Bandgap<br>Reference<br>Resistor | RREF_BG0<br>RREF_BG1 | A10<br>B10       | Analog | The connection point for the bandgap reference resistor. This should be a precision 1%, 2.00 $\mbox{K}\Omega$ resistor tied to ground |

### Table 2-17 X557-AT

| Signal Name                      | Pin Name(s) | Pin<br>Number(s) | Туре   | Description                                                                                                                           |

|----------------------------------|-------------|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| Bandgap<br>Reference<br>Resistor | RREF_BG     | A10              | Analog | The connection point for the bandgap reference resistor. This should be a precision 1%, 2.00 $\mbox{K}\Omega$ resistor tied to ground |

# 2.11 Test

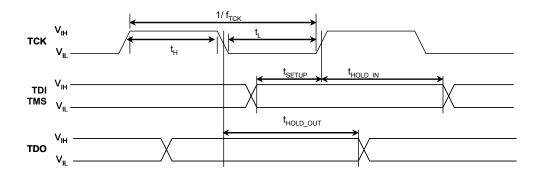

The X557 supports a IEEE 1149.1 compliant JTAG interface, with 1149.6 AC JTAG support on the SerDes interface. Note that for normal operation, TRST\_N should be held low.

| Signal Name         | Pin Name(s) | Pin<br>Number(s) | Туре | Description                                                                                                  |

|---------------------|-------------|------------------|------|--------------------------------------------------------------------------------------------------------------|

| JTAG Clock          | тск         | K14              | I    | The JTAG clock input.<br>This input is on the VDD_IO domain and has a pull-down<br>associated with it.       |

| JTAG Data<br>Input  | TDI         | L14              | I    | The JTAG data input signal.<br>This input is on the VDD_IO domain and has a pull-down<br>associated with it. |

| JTAG Data<br>Output | TDO         | L15              | 0    | The JTAG data output signal.<br>This 20 mA output is on the VDD_IO domain.                                   |

| Signal Name             | Pin Name(s) | Pin<br>Number(s) | Туре | Description                                                                                                                                          |

|-------------------------|-------------|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Reset*             | TRST_N      | M15              | I    | The JTAG reset signal. If JTAG is not used, this pin must be pulled low.<br>This input is on the VDD_IO domain and has a pull-up associated with it. |

| JTAG Test<br>Mode State | TMS         | M16              | I    | The JTAG test mode state signal.<br>This input is on the VDD_IO domain and has a pull-down<br>associated with it.                                    |

# 2.12 Metrology

The X557 contains two thermal diodes (note that the X557-AT only has one thermal diode) that can be used to monitor the die temperature without going through the MDIO registers. The "P" indicates the anode terminal (such as current input) of the thermal diode.

Table 2-18 X557-AT2

| Signal Name            | Pin Name(s)          | Pin<br>Number(s) | Туре   | Description                    |

|------------------------|----------------------|------------------|--------|--------------------------------|

| PHY 0 Thermal<br>Diode | TDIO_P_0<br>TDIO_N_0 | G3<br>F3         | Analog | PHY 0 thermal diode terminals. |

| PHY 1 Thermal<br>Diode | TDIO_P_1<br>TDIO_N_1 | F14<br>G15       | Analog | PHY 1 thermal diode terminals. |

### Table 2-19 X557-AT

| Signal Name   | Pin Name(s)          | Pin<br>Number(s) | Туре   | Description              |

|---------------|----------------------|------------------|--------|--------------------------|

| Thermal Diode | TDIO_P_0<br>TDIO_N_0 | G3<br>F3         | Analog | Thermal diode terminals. |

# 2.13 Debug

The X557 supports a side-access port to the MDIO register space via a slave SMBus. Addressing for this SMBus is provisioned on a per PHY basis. It is recommended that every design connect these SMBus pins to a header to allow in-system debug. This obviates the need to disconnect the MDIO lines, and allows for normal system operation during debug.

| Signal Name       | Pin Name(s)  | Pin<br>Number(s) | Туре | Description                                                                                                                                                                                                              |  |

|-------------------|--------------|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DebugBus<br>Clock | DebugBus_CLK | H17              | I    | Clock signal for slave SMBus used for debug port into PHY MDIO register space. This signal requires a pull-up to VDD_IO.<br>This input is on the VDD_IO domain and has a pull-down associated with it.                   |  |

| DebugBus<br>Data  | DebugBus_DAT | H18              | I/O  | Data signal for slave SMBus used for debug port into the<br>PHYs MDIO register space. This signal requires a pull-up to<br>VDD_IO.<br>This 20 mA I/O is on the VDD_IO domain and has a pull-<br>down associated with it. |  |

# 2.14 Power

The X557 uses four separate power supplies to minimize power consumption:

- 0.83V

- 1.2V

- 2.1V

- 2.5V

As mentioned earlier, in order to provide maximum flexibility to the implementation, the X557 utilizes a programmable I/O voltage. The logic thresholds for the I/O are set at 70% and 30% for VIH/VOH and VIL/VOL respectively for any VDD\_IO greater than 1.8V. For 1.2V MDIO operation (affects TX\_EN, MDC, MDIO, RST\_N), a separate signal called MDIO\_1P2\_SELECT\_N is provided that will force 1.2V operation on these signals, regardless of the VDD\_IO voltage.

### Table 2-20 X557-AT2

| Signal Name | Pin Name(s) | Pin Number(s)                                                        | Туре   | Description            |

|-------------|-------------|----------------------------------------------------------------------|--------|------------------------|

| AVDD        | VCC1P2      | D4, D6, E5, E7, E9, D11, D13, D15, E12, E14                          | Supply | 1.2V analog<br>supply. |

| AVDD22      | VCC2P1      | A3, A5, A7, A9, C3, C5, C7, C9, A12, A14, A16,<br>C12, C14, C16, D17 | Supply | 2.1V analog supply.    |

| Signal Name             | me Pin Name(s) Pin Number(s) |                                                                                                                                                                                             | Туре   | Description                                                                                                                                                                                                                                |  |

|-------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AVSS                    | AVSS                         | B3, B5, B7, B9, B12, B14, B16, C2, C4, C6, C8,<br>C11, C13, C15, C17, D3, D5, D7, D9, D12, D14,<br>D16, D18, E4, E11, E13, E15, E17, F6, F8, F10, F12,<br>G5, G7, G9, G11, H6, H8, H10, H12 | Supply | Analog ground.                                                                                                                                                                                                                             |  |

| AVSSPLL                 | VSS                          | E6, E15                                                                                                                                                                                     | Supply | Analog ground for<br>PHY PLL.                                                                                                                                                                                                              |  |

| Analog VDD              | VDD                          | E10, E16                                                                                                                                                                                    | Supply | 0.83V supply for digital circuitry in the AFE.                                                                                                                                                                                             |  |

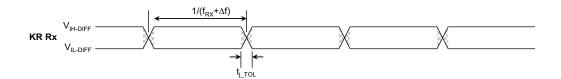

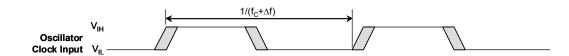

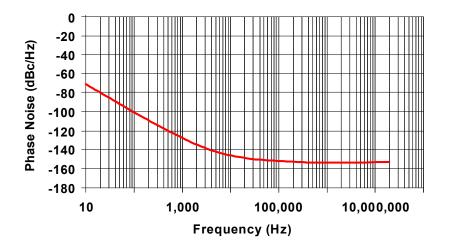

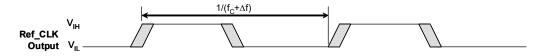

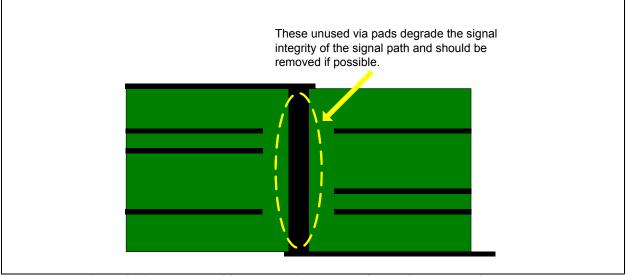

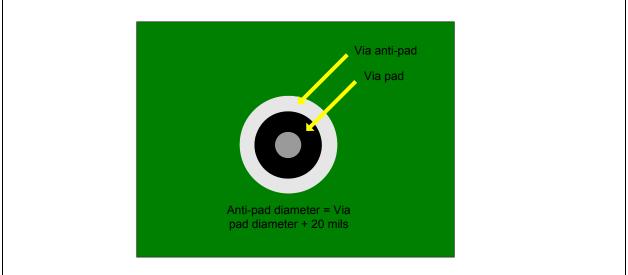

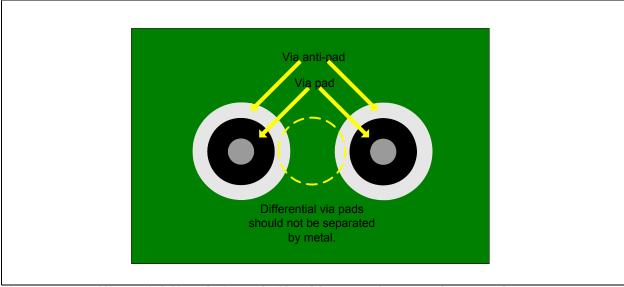

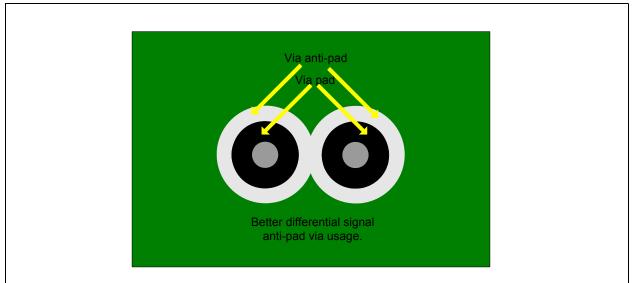

| VCC Crystal             | VCC2P1                       | E18                                                                                                                                                                                         | Supply | 2.1V supply for<br>the crystal<br>oscillator.                                                                                                                                                                                              |  |